# **Table of Contents**

| Preface                               | P-1 |

|---------------------------------------|-----|

| Who Should Use this Manual            | P-1 |

| Purpose of this Manual                | P-1 |

| Common Techniques Used in this Manual | P-5 |

| Allen–Bradley Support                 | P-5 |

# Hardware

| 1 | Installing Your Controller                                 |      |

|---|------------------------------------------------------------|------|

|   | Compliance to European Union Directives                    | 1-2  |

|   | Hardware Overview                                          | 1-2  |

|   | Master Control Relay                                       | 1-4  |

|   | Using Surge Suppressors                                    | 1-8  |

|   | Safety Considerations                                      | 1-10 |

|   | Power Considerations                                       | 1-12 |

|   | Preventing Excessive Heat                                  | 1-13 |

|   | Controller Spacing                                         | 1-14 |

|   | Mounting the Controller                                    | 1-15 |

| 2 | Wiring Your Controller                                     |      |

|   | Grounding Guidelines                                       | 2-2  |

|   | Sinking and Sourcing Circuits                              | 2-3  |

|   | Wiring Recommendations                                     | 2-4  |

|   | Wiring Diagrams, Discrete Input and Output Voltage Ranges  | 2-7  |

|   | 1761-L32AWA Wiring Diagram                                 | 2-9  |

|   | Minimizing Electrical Noise on Analog Controllers          | 2-22 |

|   | Grounding Your Analog Cable                                | 2-22 |

|   | Wiring Your Analog Channels                                | 2-23 |

|   | Analog Voltage and Current Input and Output Ranges         | 2-24 |

|   | Wiring Your Controller for High-Speed Counter Applications | 2-25 |

| 3 | Connecting the System                                      |      |

|   | Connecting the DF1 Protocol                                | 3-2  |

|   |                                                            |      |

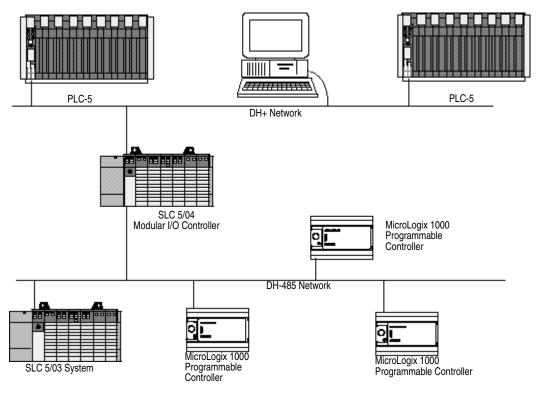

| Connecting to a DH-485 Network | 3-6  |

|--------------------------------|------|

| Connecting the AIC+            | 3-10 |

| Establishing Communication     | 3-19 |

# Programming

| 4 | Programming Overview                                          |

|---|---------------------------------------------------------------|

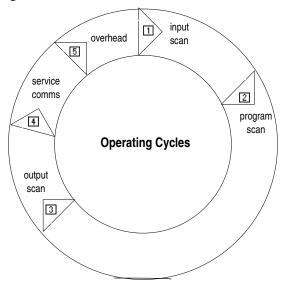

|   | Principles of Machine Control                                 |

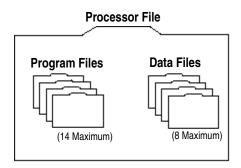

|   | Understanding File Organization                               |

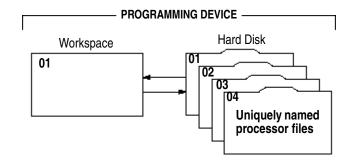

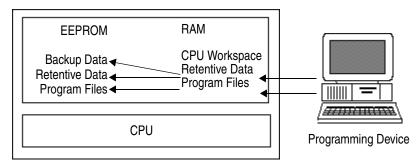

|   | Understanding How Processor Files are Stored and Accessed 4-6 |

|   | Addressing Data Files 4-10                                    |

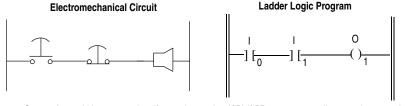

|   | Applying Ladder Logics to Your Schematics                     |

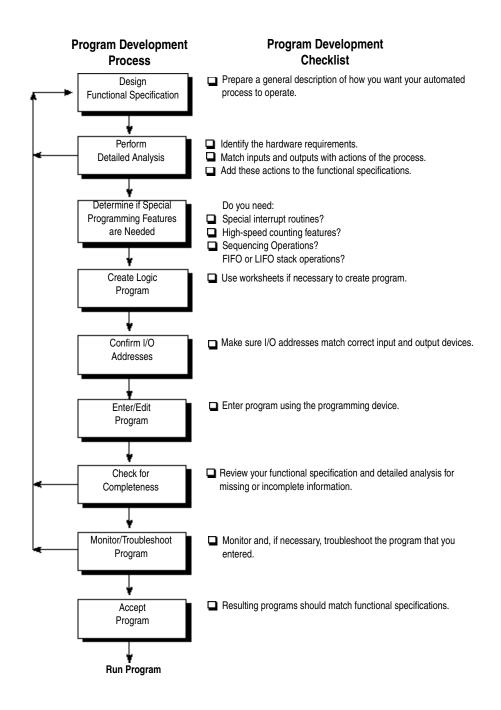

|   | Developing Your Logic Program - A Model                       |

| 5 | Using Analog                                                  |

|   | I/O Image                                                     |

|   | I/O Configuration                                             |

|   | Input Filter and Update Times                                 |

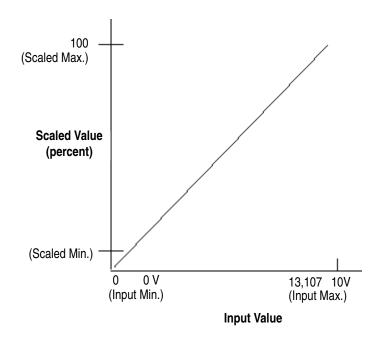

|   | Converting Analog Data                                        |

| 6 | Using Basic Instructions                                      |

|   | About the Basic Instructions                                  |

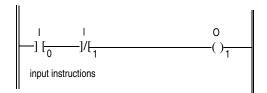

|   | Bit Instructions Overview                                     |

|   | Examine if Closed (XIC)6-3                                    |

|   | Examine if Open (XIO)                                         |

|   | Output Energize (OTE)6-4                                      |

|   | Output Latch (OTL) and Output Unlatch (OTU)                   |

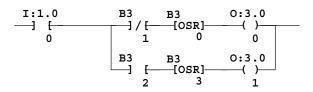

|   | One-Shot Rising (OSR)6-6                                      |

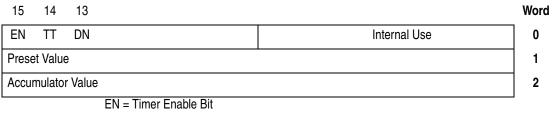

|   | Timer Instructions Overview                                   |

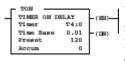

|   | Timer On–Delay (TON)6-10                                      |

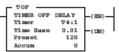

|   | Timer Off–Delay (TOF)6-11                                     |

|   | Retentive Timer (RTO)6-13                                     |

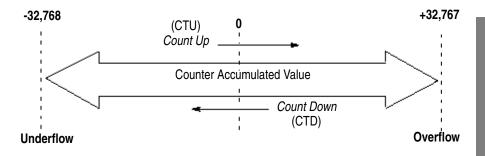

|   | Counter Instructions Overview                                 |

|   | Count Up (CTU)                                                |

|   | Count Down (CTD)                                              |

|   | Reset (RES)                                                   |

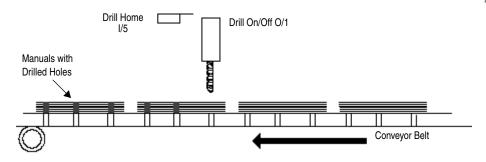

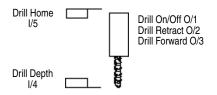

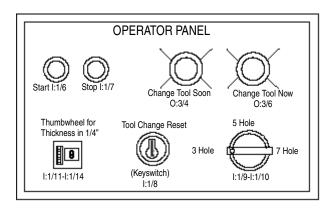

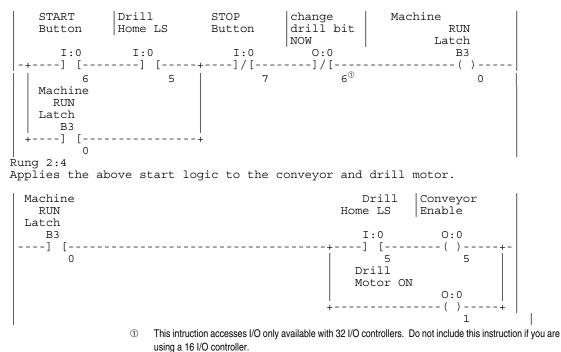

|   | Basic Instructions in the Paper Drilling Machine Application Example 6-2       | 21           |

|---|--------------------------------------------------------------------------------|--------------|

| 7 | Using Comparison Instructions                                                  |              |

|   | About the Comparison Instructions                                              | ·-2          |

|   | Comparison Instructions Overview7                                              | '-2          |

|   | Equal (EQU)                                                                    | <b>'-</b> 3  |

|   | Not Equal (NEQ)                                                                | <b>'-</b> 3  |

|   | Less Than (LES)                                                                | ' <b>-</b> 3 |

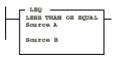

|   | Less Than or Equal (LEQ)                                                       | ' <b>-</b> 4 |

|   | Greater Than (GRT)7                                                            |              |

|   | Greater Than or Equal (GEQ)                                                    |              |

|   | Masked Comparison for Equal (MEQ)                                              | '-5          |

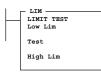

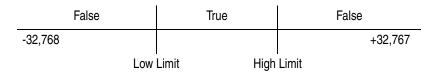

|   | Limit Test (LIM)7                                                              |              |

|   | Comparison Instructions in the Paper Drilling Machine Application Examp<br>7-8 | le           |

| 8 | Using Math Instructions                                                        |              |

| 0 | About the Math Instructions                                                    | , n          |

|   | Math Instructions Overview                                                     |              |

|   | Add (ADD)                                                                      |              |

|   | Subtract (SUB)                                                                 |              |

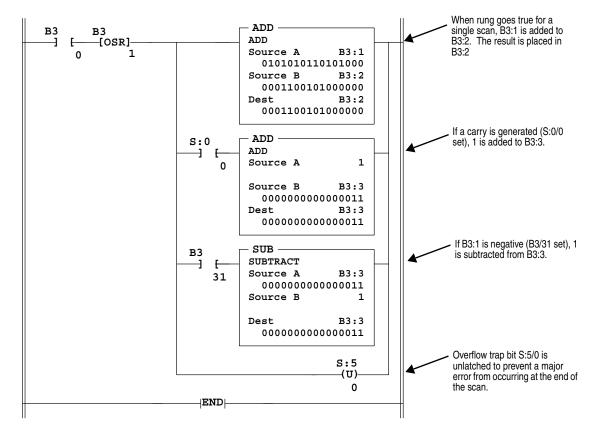

|   | 32–Bit Addition and Subtraction                                                |              |

|   | Multiply (MUL)                                                                 |              |

|   | Divide (DIV)                                                                   |              |

|   | Double Divide (DDV)                                                            |              |

|   | Clear (CLR)                                                                    |              |

|   | Square Root (SQR)                                                              |              |

|   | Scale Data (SCL)                                                               |              |

|   | Math Instructions in the Paper Drilling Machine Application Example . 8-       |              |

| 9 | Using Data Handling Instructions                                               |              |

|   | About the Data Handling Instructions.                                          | )-2          |

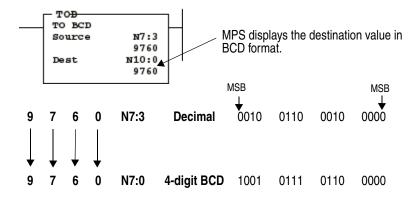

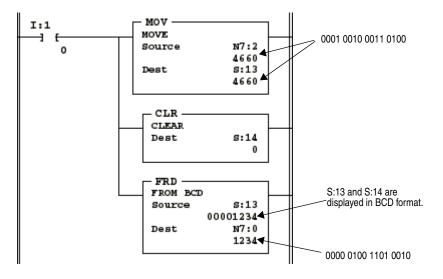

|   | Convert to BCD (TOD)                                                           | )-3          |

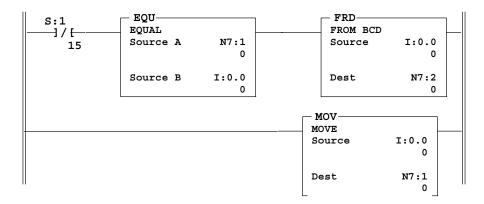

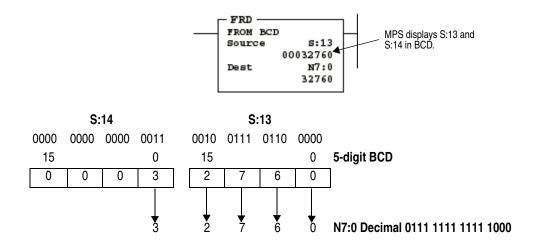

|   | Convert from BCD (FRD)9                                                        | )-4          |

|   | Decode 4 to 1 of 16 (DCD)                                                      | )-8          |

|   | Encode 1 of 16 to 4 (ENC) 9                                                    | -9           |

|   | Copy File (COP) and Fill File (FLL) Instructions                               | 10           |

|   | Move and Logical Instructions Overview                                         | 13           |

|   |                                                                                |              |

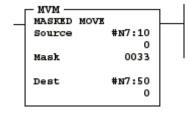

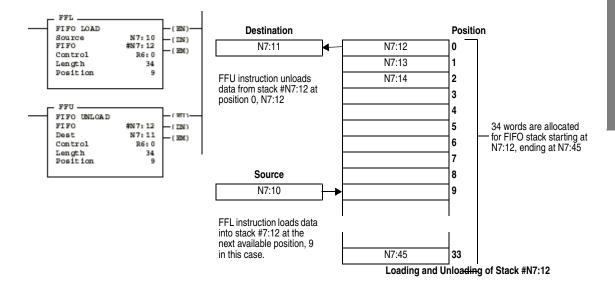

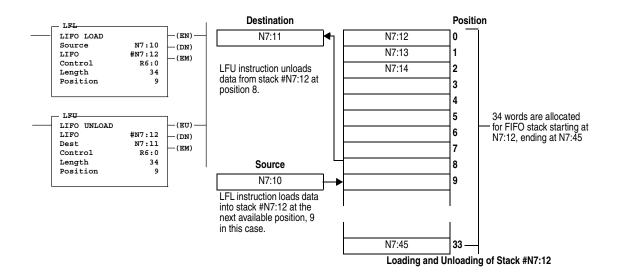

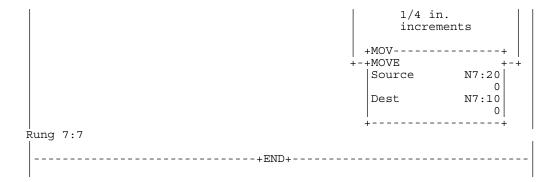

|    | Move (MOV)Masked Move (MVM)And (AND)Or (OR)Exclusive Or (XOR)Not (NOT)Negate (NEG)FIFO and LIFO Instructions OverviewFIFO Load (FFL) and FIFO Unload (FFU)LIFO Load (LFL) and LIFO Unload (LFU)Data Handling Instructions in the Paper Drilling Machine ApplicExample | 9-16<br>9-18<br>9-19<br>9-20<br>9-21<br>9-22<br>9-23<br>9-25<br>9-26<br>cation |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 10 | Using Program Flow Control Instructions                                                                                                                                                                                                                               |                                                                                |

| 10 | About the Program Flow Control Instructions                                                                                                                                                                                                                           | 10-2                                                                           |

|    | Jump (JMP) and Label (LBL)                                                                                                                                                                                                                                            |                                                                                |

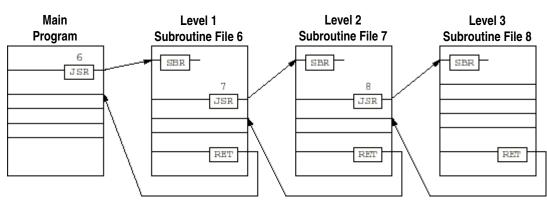

|    | Jump to Subroutine (JSR), Subroutine (SBR), and Return (RE                                                                                                                                                                                                            |                                                                                |

|    | Master Control Reset (MCR)                                                                                                                                                                                                                                            | 10-7                                                                           |

|    | Temporary End (TND)                                                                                                                                                                                                                                                   |                                                                                |

|    | Suspend (SUS)                                                                                                                                                                                                                                                         |                                                                                |

|    | Immediate Input with Mask (IIM)                                                                                                                                                                                                                                       |                                                                                |

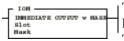

|    | Immediate Output with Mask (IOM)                                                                                                                                                                                                                                      |                                                                                |

|    | Program Flow Control Instructions in the Paper Drilling Machine Example                                                                                                                                                                                               |                                                                                |

| 11 | Using Application Specific Instructions                                                                                                                                                                                                                               |                                                                                |

|    | About the Application Specific Instructions                                                                                                                                                                                                                           | 11.0                                                                           |

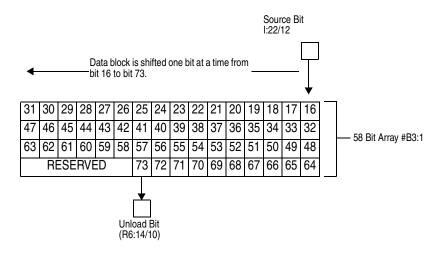

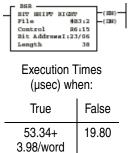

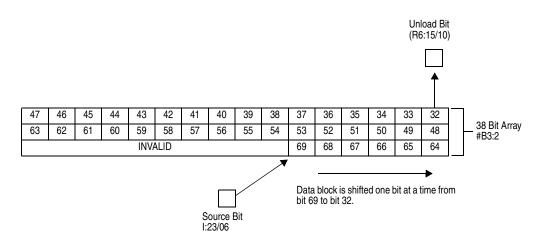

|    | Bit Shift Instructions Overview                                                                                                                                                                                                                                       |                                                                                |

|    | Bit Shift Left (BSL)                                                                                                                                                                                                                                                  |                                                                                |

|    | Bit Shift Right (BSR).                                                                                                                                                                                                                                                |                                                                                |

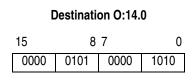

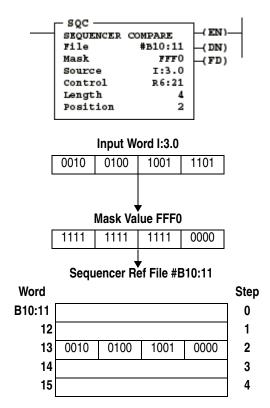

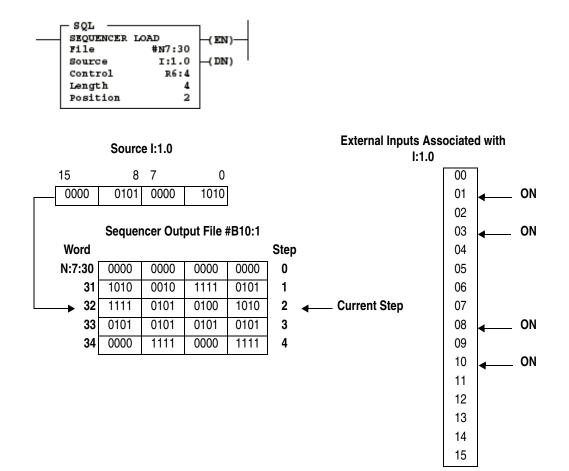

|    | Sequencer Instructions Overview                                                                                                                                                                                                                                       |                                                                                |

|    | Sequencer Output (SQO) and Sequencer Compare (SQC)                                                                                                                                                                                                                    | 11-7                                                                           |

|    | Sequencer Load (SQL)                                                                                                                                                                                                                                                  |                                                                                |

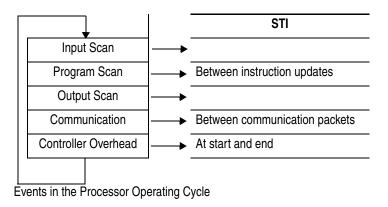

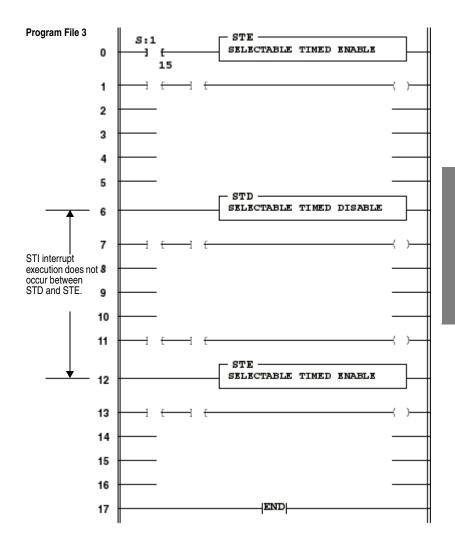

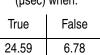

|    | Selectable Timed Interrupt (STI) Function Overview                                                                                                                                                                                                                    |                                                                                |

|    | Selectable Timed Disable (STD) and Enable (STE)                                                                                                                                                                                                                       |                                                                                |

|    | Selectable Timed Start (STS)                                                                                                                                                                                                                                          |                                                                                |

|    | Interrupt Subroutine (INT)                                                                                                                                                                                                                                            | 11-22                                                                          |

|    | Application Specific Instructions in the Paper Drilling Machine Application<br>Example |

|----|----------------------------------------------------------------------------------------|

| 12 | Using High–Speed Counter Instructions                                                  |

|    | About the High–Speed Counter Instructions                                              |

|    | High–Speed Counter Instructions Overview                                               |

|    | High–Speed Counter (HSC)                                                               |

|    | High–Speed Counter Load (HSL) 12-18                                                    |

|    | High–Speed Counter Reset (RES)                                                         |

|    | High–Speed Counter Reset Accumulator (RAC)                                             |

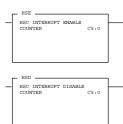

|    | High–Speed Counter Interrupt Enable (HSE) and Disable (HSD) 12-23                      |

|    | Update High–Speed Counter Image Accumulator (OTE) 12-24                                |

|    | What Happens to the HSC When Going to REM Run Mode 12-25                               |

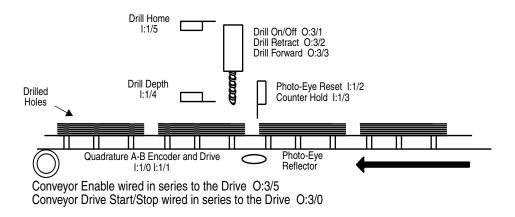

|    | High-Speed Counter Instruction in the Paper Drilling Machine Application               |

|    | Example                                                                                |

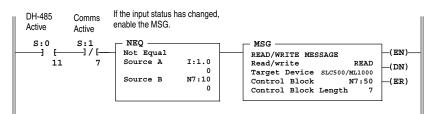

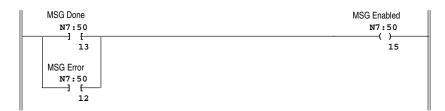

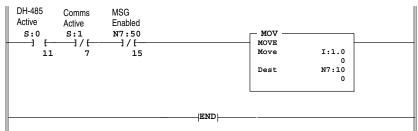

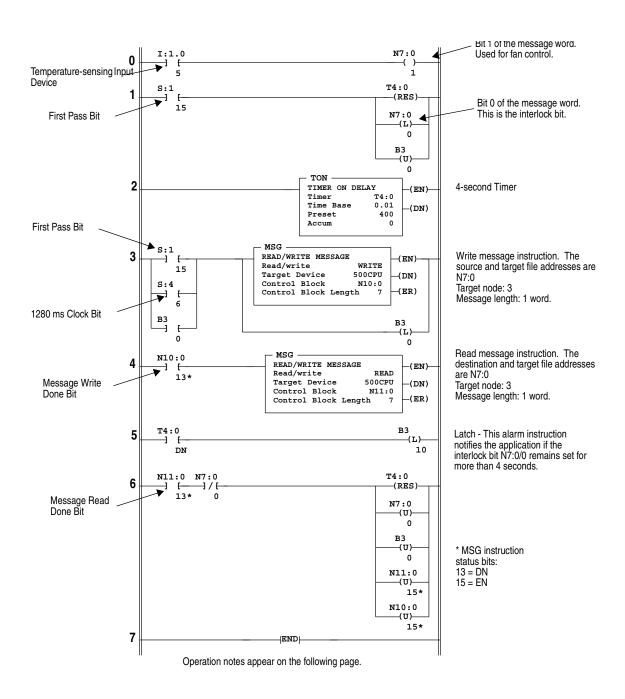

| 13 | Using the Message Instruction                                                          |

|    | Types of Communication                                                                 |

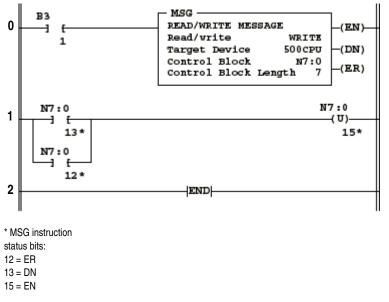

|    | Message Instruction (MSG) 13-3                                                         |

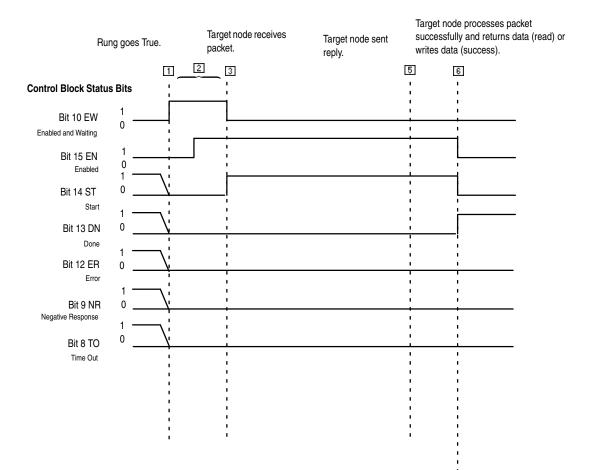

|    | Timing Diagram for a Successful MSG Instruction                                        |

|    | MSG Instruction Error Codes                                                            |

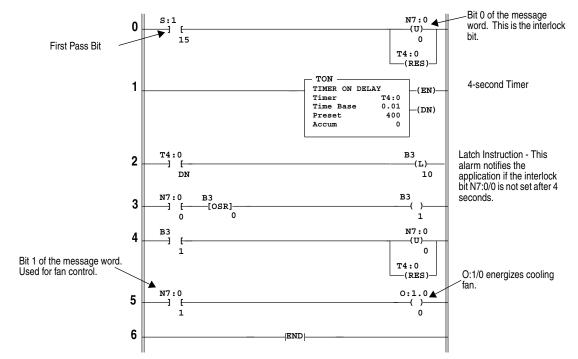

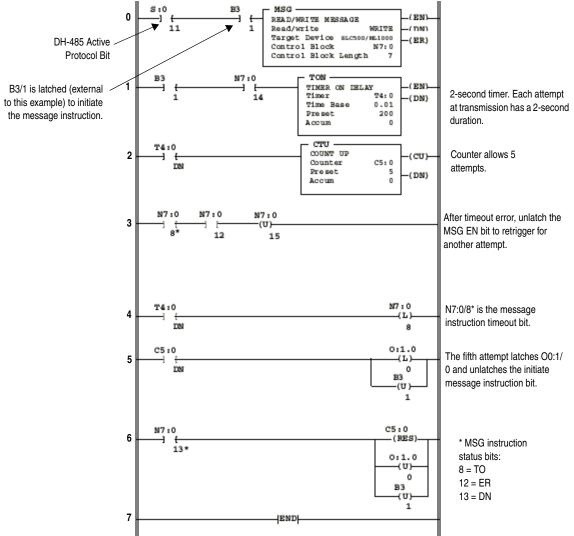

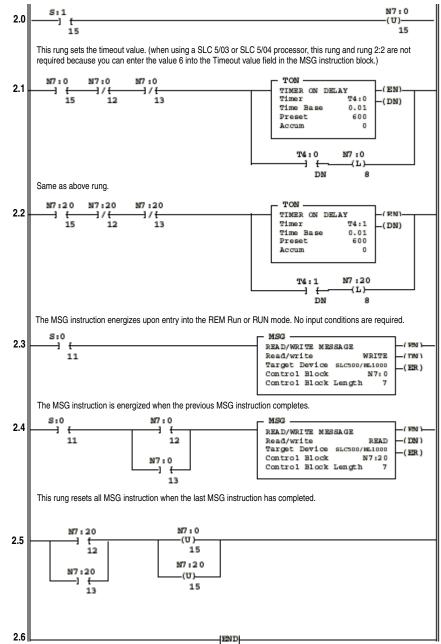

|    | Application Examples that Use the MSG Instruction                                      |

|    |                                                                                        |

# Troubleshooting

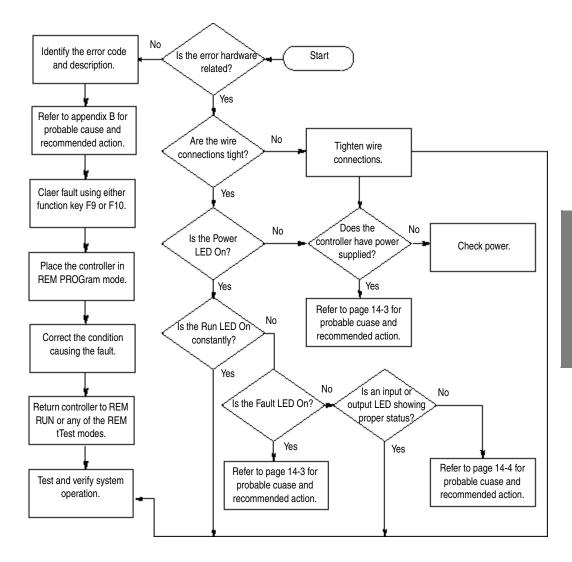

| 14 | Troubleshooting Your System             |      |

|----|-----------------------------------------|------|

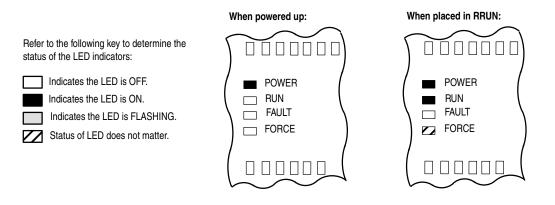

|    | Understanding the Controller LED Status | 14-2 |

|    | Controller Error Recovery Model         | 14-5 |

|    | Identifying Controller Faults           | 14-6 |

| Identifying Controller Faults        |   | 14-6 |

|--------------------------------------|---|------|

| Calling Allen-Bradley for Assistance | 1 | 4-11 |

# Reference

| Α | Hardware Reference                                               |   |

|---|------------------------------------------------------------------|---|

|   | Controller SpecificationsA-2                                     | 2 |

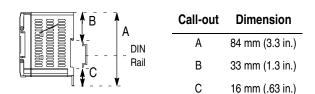

|   | Controller DimensionsA-1                                         | 1 |

|   | Replacement Parts A-12                                           | 2 |

| В | Programming Reference                                            |   |

|   | Controller Status FileB-1                                        | 1 |

|   | Instruction Execution Times and Memory UsageB-25                 | 5 |

| С | Valid Addressing Modes and File Types for Instruction Parameters |   |

|   | Available File Types                                             |   |

|   | Available Addressing ModesC-2                                    |   |

| D | Understanding the Communication                                  |   |

|   | Protocols                                                        |   |

|   | RS-232 Communication InterfaceD-1                                | 1 |

|   | DF1 Full-Duplex Protocol                                         | 2 |

|   | DF1 Half-Duplex Slave ProtocolD-5                                | 5 |

|   | DH–485 Communication ProtocolD-10                                | ) |

| E | Application Example Programs                                     |   |

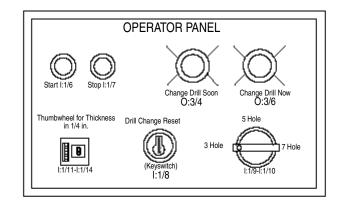

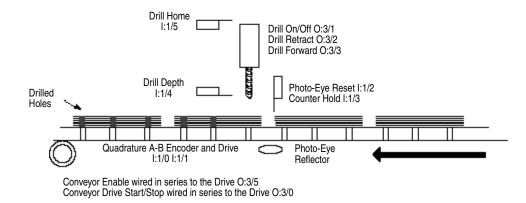

|   | Paper Drilling Machine Application Example E-2                   | 2 |

|   | Time Driven Sequencer Application Example                        | 7 |

|   | Event Driven Sequencer Application ExampleE-19                   | 9 |

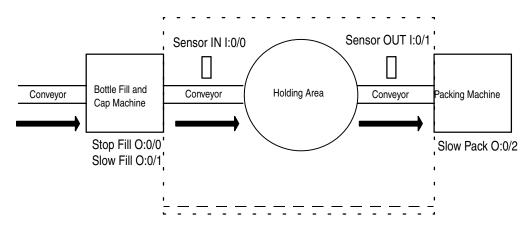

|   | Bottle Line Example E-2 <sup>-</sup>                             | 1 |

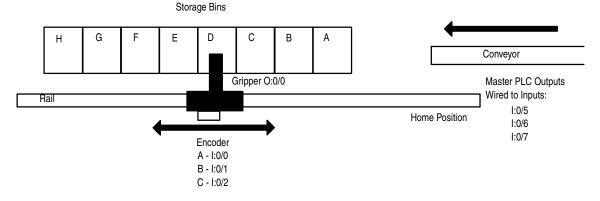

|   | Pick and Place Machine Example                                   |   |

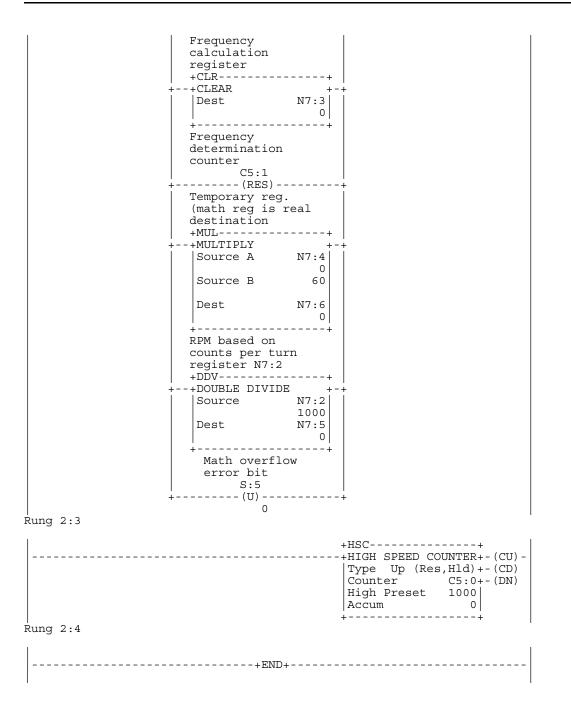

|   | RPM Calculation Application Example                              |   |

|   | On/Off Circuit ExampleE-34                                       |   |

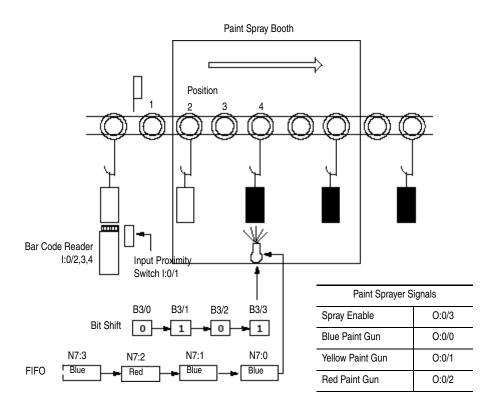

|   | Spray Booth Application ExampleE-36                              |   |

|   | Adjustable Timer Application ExampleE-4 <sup>-</sup>             | 1 |

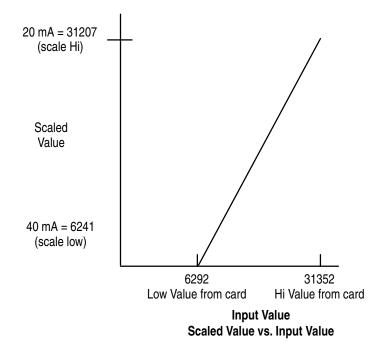

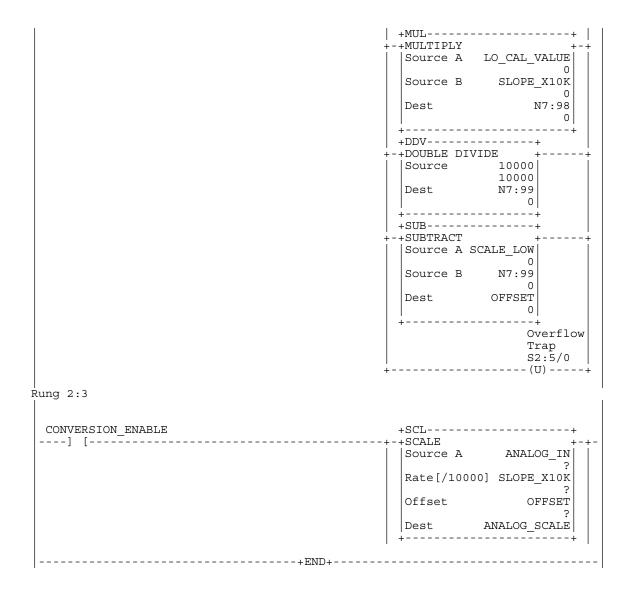

| F | Optional Analog Input Software Calibration                       |   |

|   | Calibrating an Analog Input Channel                              |   |

|   | GlossaryG-1                                                      |   |

|   | IndexH-1                                                         | 1 |

# **Summary of Changes**

The information below summarizes the changes to this manual since the last printing as Publication 1761-6.3 — July 1998.

To help you find new information and updated information in this release of the manual, we have included change bars as shown to the right of this paragraph.

## **New Information**

The table below lists sections that document new features and additional information about existing features, and shows where to find this new information.

| For This New Information                                 | See       |

|----------------------------------------------------------|-----------|

| Updated explosion hazard information                     | page 1-15 |

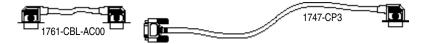

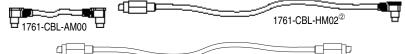

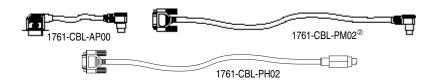

| Added 1761-CBL-AH02 and 1761-CBL-PH02 to cable selection | page 3-14 |

| Removed catalog 1761-NET-DNI                             | Chapter 3 |

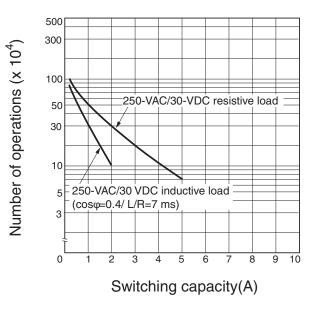

| Updated relay life specifications                        | page A-6  |

| Added relay life chart                                   | page A-6  |

# **Updated Information**

Changes from the previous release of this manual that require you to reference information differently are as follows:

- The DeviceNet communications information has been updated; see chapter 3, Connecting the System.

- For updated information on automatic protocol switching, see chapter 3, Connecting the System.

- The MicroLogix<sup>TM</sup> 1000 programmable controllers' VA ratings and power supply inrush specifications have been updated; see appendix A, Hardware Reference.

• The DF1 Full–Duplex and DH–485 configuration parameters have been updated; see appendix D, Understanding Communication Protocols.

# Preface

Read this preface to familiarize yourself with the rest of the manual. It provides information concerning:

- who should use this manual

- the purpose of this manual

- conventions used in this manual

- Allen–Bradley support

### Who Should Use this Manual

Use this manual if you are responsible for designing, installing, programming, or troubleshooting control systems that use MicroLogix<sup>TM</sup> 1000 controllers.

You should have a basic understanding of electrical circuitry and familiarity with relay logic. If you do not, obtain the proper training before using this product.

#### **Purpose of this Manual**

This manual is a reference guide for MicroLogix<sup>™</sup> 1000 controllers. It describes the procedures you use to install, wire, program, and troubleshoot your controller. This manual:

- · explains how to install and wire your controllers

- gives you an overview of the MicroLogix<sup>™</sup> 1000 controller system

- provides the MicroLogix<sup>™</sup> 1000 controllers' instruction set

- contains application examples to show the instruction set in use

See your programming software user manual for information on programming your MicroLogix<sup>TM</sup> 1000 controller. For information on using the Hand-Held Programmer with the MicroLogix<sup>TM</sup> 1000 controllers, see the *MicroLogix<sup>TM</sup> 1000 with Hand-Held Programmer (HHP) User Manual*, Publication 1761-6.2.

### **Contents of this Manual**

| Tab         | Chapter | Title                                      | Contents                                                                                                                                           |

|-------------|---------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|             |         | Preface                                    | Describes the purpose, background, and scope of this manual. Also specifies the audience for whom this manual is intended.                         |

|             | 1       | Installing Your<br>Controller              | Provides controller installation procedures and system safety considerations.                                                                      |

| Hardware    | 2       | Wiring Your Controller                     | Provides wiring guidelines and diagrams.                                                                                                           |

|             | 3       | Connecting the<br>System                   | Gives information on wiring your controller system for the DF1 protocol or DH–485 network.                                                         |

|             | 4       | Programming<br>Overview                    | Provides an overview of principles of machine control, a section on file organization and addressing, and a program development model.             |

|             | 5       | Using Analog                               | Provides information on I/O image file format, I/O configuration, input filter and update times, and conversion of analog data.                    |

|             | 6       | Using Basic<br>Instructions                | Describes how to use ladder logic instructions for relay replacement functions, counting, and timing.                                              |

|             | 7       | Using Comparison<br>Instructions           | Describes how to use the instructions to compare values of data in your ladder logic program.                                                      |

| Programming | 8       | Using Math<br>Instructions                 | Describes how to use the ladder logic instructions that perform basic math functions.                                                              |

|             | 9       | Using Data Handling<br>Instructions        | Describes how to perform data handling instructions,<br>including move and logical instructions and FIFO and LIFO<br>instructions.                 |

|             | 10      | Using Program Flow<br>Control Instructions | Describes the ladder logic instructions that affect program flow and execution.                                                                    |

|             | 11      | Using Application<br>Specific Instructions | Describes the bit shift, sequencer and STI related instructions.                                                                                   |

|             | 12      | Using High-Speed<br>Counter Instructions   | Describes the four modes of the high-speed counter and its related instructions.                                                                   |

|             | 13      | Using the Message<br>Instruction           | Provides a general overview of the types of communication<br>and explains how to establish network communication using<br>the message instruction. |

| Tab             | Chapter    | Title                                                                     | Contents                                                                                                           |

|-----------------|------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Troubleshooting | 14         | Troubleshooting Your<br>System                                            | Explains how to interpret and correct problems with your MicroLogix <sup>TM</sup> 1000 controller system.          |

|                 | Appendix A | Hardware Reference                                                        | Provides physical, electrical, environmental, and functional specifications.                                       |

|                 | Appendix B | Programming<br>Reference                                                  | Explains the system status file and provides instruction execution times.                                          |

| Reference       | Appendix C | Valid Addressing<br>Modes and File Types<br>for Instruction<br>Parameters | Provides a listing of the instructions along with their parameters and valid file types.                           |

|                 | Appendix D | Understanding the<br>Communication<br>Protocols                           | Contains descriptions of the DF1 protocol and DH-485 network.                                                      |

|                 | Appendix E | Application Example<br>Programs                                           | Provides advanced application examples for the high-speed counter, sequencer, bit shift, and message instructions. |

|                 | Appendix F | Optional Analog Input<br>Software Calibration                             | Explains how to calibrate your controller using software offsets.                                                  |

|                 |            | Glossary                                                                  | Contains definitions for terms and abbreviations that are specific to this product.                                |

## **Related Documentation**

The following documents contain additional information concerning Allen–Bradley products. To obtain a copy, contact your local Allen–Bradley office or distributor.

| For                                                                                                                                                                                              | Read this Document                                                              | Document<br>Number |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------|

| A procedural manual for technical personnel who use the Allen–Bradley Hand–Held Programmer (HHP) to monitor and develop control logic programs for the MicroLogix <sup>TM</sup> 1000 controller. | MicroLogix <sup>™</sup> 1000 with Hand–<br>Held Programmer (HHP) User<br>Manual | 1761-6.2           |

| For                                                                                                                                                               | Read this Document                                                                                | Document<br>Number                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Information on mounting and wiring the MicroLogix <sup>TM</sup><br>1000 controllers, including a mounting template for easy<br>installation                       | MicroLogix <sup>TM</sup> 1000<br>Programmable Controllers<br>Installation Instructions            | 1761–5.1.2                                                                       |

|                                                                                                                                                                   | MicroLogix <sup>TM</sup> 1000 (Analog)<br>Programmable Controllers<br>Installation Instructions   | 1761–5.1.3                                                                       |

| The procedures necessary to install and connect the AIC+ and DNI                                                                                                  | Advanced Interface Converter<br>(AIC+) and DeviceNet Interface<br>(DNI) Installation Instructions | 1761–5.11                                                                        |

| A description on how to install and connect an AIC+. This manual also contains information on network wiring.                                                     | Advanced Interface Converter<br>(AIC+) User Manual                                                | 1761–6.4                                                                         |

| Information on how to install, configure, and commission a DNI                                                                                                    | DeviceNet <sup>™</sup> Interface User Manual                                                      | 1761–6.5                                                                         |

| In–depth information on grounding and wiring Allen–Bradley programmable controllers                                                                               | Allen–Bradley Programmable<br>Controller Grounding and Wiring<br>Guidelines                       | 1770–4.1                                                                         |

| A description of important differences between solid–state<br>programmable controller products and hard–wired<br>electromechanical devices                        | Application Considerations for Solid–<br>State Controls                                           | SGI-1.1                                                                          |

| An article on wire sizes and types for grounding electrical equipment                                                                                             | National Electrical Code                                                                          | Published by<br>the National<br>Fire Protection<br>Association of<br>Boston, MA. |

| A complete listing of current documentation, including ordering instructions. Also indicates whether the documents are available on CD–ROM or in multi–languages. | Allen–Bradley Publication Index                                                                   | SD499                                                                            |

| A glossary of industrial automation terms and abbreviations                                                                                                       | Allen–Bradley Industrial Automation Glossary                                                      | AG-7.1                                                                           |

| Information on understanding and applying MicroLogix <sup>TM</sup> 1000 controllers                                                                               | MicroMentor                                                                                       | 1761-MMB                                                                         |

# **Common Techniques Used in this Manual**

The following conventions are used throughout this manual:

- Bulleted lists such as this one provide information, not procedural steps.

- Numbered lists provide sequential steps or hierarchical information.

- *Italic* type is used for emphasis.

## Allen–Bradley Support

Allen–Bradley offers support services worldwide, with over 75 Sales/Support Offices, 512 authorized Distributors and 260 authorized Systems Integrators located throughout the United States alone, plus Allen–Bradley representatives in every major country in the world.

#### **Local Product Support**

Contact your local Allen-Bradley representative for:

- sales and order support

- product technical training

- warranty support

- support service agreements

#### **Technical Product Assistance**

If you need to contact Allen–Bradley for technical assistance, please review the information in the *Troubleshooting* chapter first. Then call your local Allen–Bradley representative.

#### Your Questions or Comments on this Manual

If you find a problem with this manual, or you have any suggestions for how this manual could be made more useful to you, please contact us at the address below:

Allen–Bradley Company, Inc. Control and Information Group Technical Communication, Dept. 602V, T122 P.O. Box 2086 Milwaukee, WI 53201–2086

or visit our internet page at:

#### http://www.ab.com/micrologix

# Installing Your Controller

This chapter shows you how to install your controller system. The only tools you require are a Flat head or Phillips head screwdriver and drill. Topics include:

- compliance to European Union Directives

- hardware overview

- master control relay

- surge suppressors

- safety considerations

- power considerations

- preventing excessive heat

- controller spacing

- mounting the controller

# **Compliance to European Union Directives**

If this product has the CE mark it is approved for installation within the European Union and EEA regions. It has been designed and tested to meet the following directives.

#### **EMC** Directive

This product is tested to meet Council Directive 89/336/EEC Electromagnetic Compatibility (EMC) and the following standards, in whole or in part, documented in a technical construction file:

- EN 50081-2 EMC – Generic Emission Standard, Part 2 – Industrial Environment

- EN 50082-2 EMC – Generic Immunity Standard, Part 2 – Industrial Environment

This product is intended for use in an industrial environment.

## **Hardware Overview**

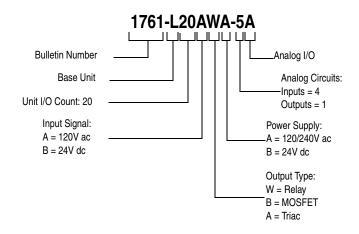

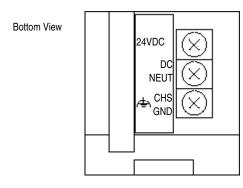

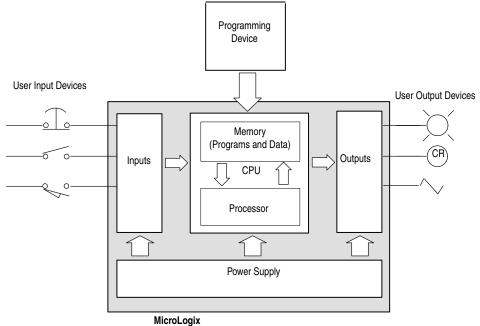

The MicroLogix 1000 programmable controller is a packaged controller containing a power supply, input circuits, output circuits, and a processor. The controller is available in 10 I/O, 16 I/O and 32 I/O configurations, as well as an analog version with 20 discrete I/O and 5 analog I/O.

The catalog number for the controller is composed of the following:

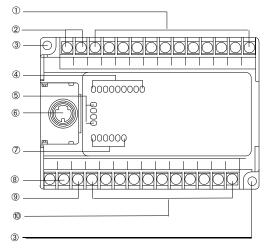

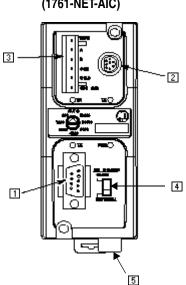

The hardware features of the controller are:

- 1 Input terminals

- ② dc output terminals (or not used)

- ③ Mounting hole

- ④ Input LEDs

- Status LEDs

- 6 RS-232 communication channel

- ⑦ Output LEDs

- 8 Power supply line power

- Ground screw

- Output terminals

# **Master Control Relay**

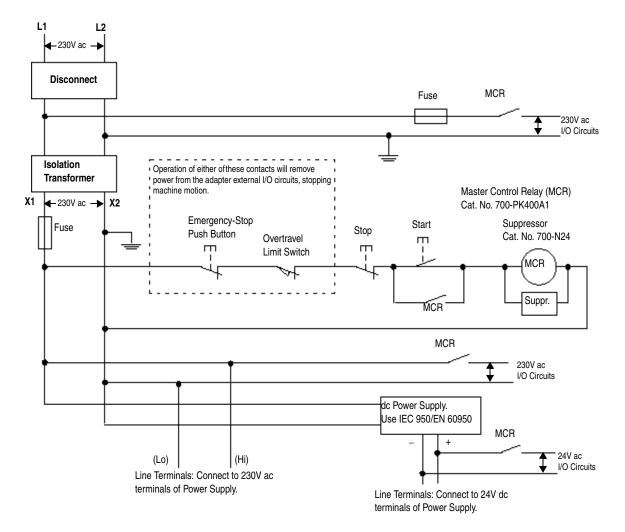

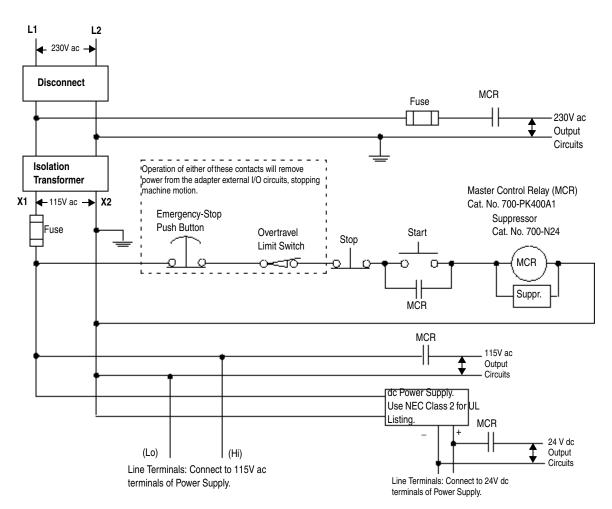

A hard-wired master control relay (MCR) provides a reliable means for emergency controller shutdown. Since the master control relay allows the placement of several emergency-stop switches in different locations, its installation is important from a safety standpoint. Overtravel limit switches or mushroom head push buttons are wired in series so that when any of them opens, the master control relay is de-energized. This removes power to input and output device circuits. Refer to the figure on page 1-6.

**ATTENTION:** Never alter these circuits to defeat their function, since serious injury and/or machine damage could result.

**Note:** If you are using an external dc output power supply, interrupt the dc output side rather than the ac line side of the supply to avoid the additional delay of power supply turn-off.

The external ac line of the dc output power supply should be fused.

Connect a set of master control relays in series with the dc power supplying the input and output circuits.

Place the main power disconnect switch where operators and maintenance personnel have quick and easy access to it. If you mount a disconnect switch inside the controller enclosure, place the switch operating handle on the outside of the enclosure, so that you can disconnect power without opening the enclosure.

Whenever any of the emergency-stop switches are opened, power to input and output devices should be removed.

When you use the master control relay to remove power from the external I/O circuits, power continues to be provided to the controller's power supply so that diagnostic indicators on the processor can still be observed.

The master control relay is not a substitute for a disconnect to the controller. It is intended for any situation where the operator must quickly de-energize I/O devices only. When inspecting or installing terminal connections, replacing output fuses, or working on equipment within the enclosure, use the disconnect to shut off power to the rest of the system.

**Note:** Do not control the master control relay with the controller. Provide the operator with the safety of a direct connection between an emergency-stop switch and the master control relay.

#### **Using Emergency-Stop Switches**

When using emergency-stop switches, adhere to the following points:

- Do not program emergency-stop switches in the controller program. Any emergency-stop switch should turn off all machine power by turning off the master control relay.

- Observe all applicable local codes concerning the placement and labeling of emergency-stop switches.

- Install emergency-stop switches and the master control relay in your system. Make certain that relay contacts have a sufficient rating for your application. emergency-stop switches must be easy to reach.

- In the following illustration, input and output circuits are shown with MCR protection. However, in most applications, only output circuits require MCR protection.

The following illustrations show the Master Control Relay wired in a grounded system.

**Note:** The illustrations only show output circuits with MCR protection. In most applications input circuits do not require MCR protection; however, if you need to remove power from all field devices, you must include MCR contacts in series with input power wiring.

## Schematic (Using IEC Symbols)

## Schematic (Using ANSI/CSA Symbols)

# **Using Surge Suppressors**

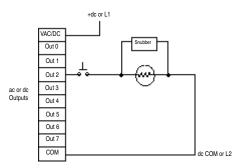

Inductive load devices such as motor starters and solenoids require the use of some type of surge suppression to protect the controller output contacts. Switching inductive loads without surge suppression can *significantly* reduce the lifetime of relay contacts. By adding a suppression device directly across the coil of an inductive device, you will prolong the life of the switch contacts. You will also reduce the effects of voltage transients caused by interrupting the current to that inductive device, and will prevent electrical noise from radiating into system wiring.

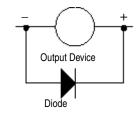

The following diagram shows an output with a suppression device. We recommend that you locate the suppression device as close as possible to the load device.

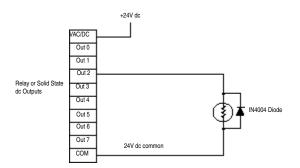

If you connect a micro controller FET output to an inductive load, we recommend that you use an IN4004 diode for surge suppression, as shown in the illustration that follows.

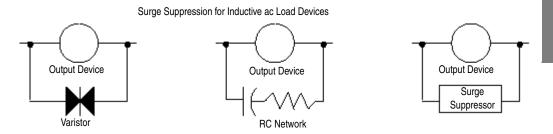

Suitable surge suppression methods for inductive ac load devices include a varistor, an RC network, or an Allen-Bradley surge suppressor, all shown below. These components must be appropriately rated to suppress the switching transient characteristic of the particular inductive device. See the table on page 1-10 for recommended suppressors.

If you connect a micro controller triac output to control an inductive load, we recommend that you use varistors to suppress noise. Choose a varistor that is appropriate for the application. The suppressors we recommend for triac outputs when switching 120V ac inductive loads are a Harris MOV, part number V175 LA10A, or an Allen-Bradley MOV, catalog number 599–K04 or 599–KA04. Consult the varistor manufacturer's data sheet when selecting a varistor for your application.

For inductive dc load devices, a diode is suitable. An 1N4004 diode is acceptable for most applications. A surge suppressor can also be used. See the table on page 1-10 for recommended suppressors.

As shown in the illustration below, these surge suppression circuits connect directly across the load device. This reduces arcing of the output contacts. (High transient can cause arcing that occurs when switching off an inductive device.)

Surge Suppression for Inductive dc Load Devices

(A surge suppressor can also be used.)

#### **Recommended Surge Suppressors**

| We recommend the Allen-Bradley surge suppressors shown in the following table for |

|-----------------------------------------------------------------------------------|

| use with Allen-Bradley relays, contactors, and starters.                          |

| Device                                                        | Coil Voltage       | Suppressor Catalog<br>Number |

|---------------------------------------------------------------|--------------------|------------------------------|

| Bulletin 509 Motor Starter                                    | 120V ac            | 599–K04                      |

| Bulletin 509 Motor Starter                                    | 240V ac            | 599–KA04                     |

| Bulletin 100 Contactor                                        | 120V ac            | 199–FSMA1                    |

| Bulletin 100 Contactor                                        | 240V ac            | 199–FSMA2                    |

| Bulletin 709 Motor Starter                                    | 120V ac            | 1401–N10                     |

| Bulletin 700 Type R, RM Relays                                | ac coil            | None Required                |

| Bulletin 700 Type R Relay                                     | 12V dc             | 700–N22                      |

| Bulletin 700 Type RM Relay                                    | 12V dc             | 700–N28                      |

| Bulletin 700 Type R Relay                                     | 24V dc             | 700–N10                      |

| Bulletin 700 Type RM Relay                                    | 24V dc             | 700–N13                      |

| Bulletin 700 Type R Relay                                     | 48V dc             | 700–N16                      |

| Bulletin 700 Type RM Relay                                    | 48V dc             | 700–N17                      |

| Bulletin 700 Type R Relay                                     | 115-125V dc        | 700–N11                      |

| Bulletin 700 Type RM Relay                                    | 115-125V dc        | 700–N14                      |

| Bulletin 700 Type R Relay                                     | 230-250V dc        | 700–N12                      |

| Bulletin 700 Type RM Relay                                    | 230-250V dc        | 700–N15                      |

| Bulletin 700 Type N, P, or PK Relay                           | 150V max, ac or DC | 700–N24                      |

| Miscellaneous electromagnetic devices limited to 35 sealed VA | 150V max, ac or DC | 700–N24                      |

# **Safety Considerations**

Safety considerations are an important element of proper system installation. Actively thinking about the safety of yourself and others, as well as the condition of your equipment, is of primary importance. We recommend reviewing the following safety considerations.

#### **Disconnecting Main Power**

**ATTENTION:** Explosion Hazard - Do not replace components or disconnect equipment unless power has been switched off and the area is known to be non-hazardous.

The main power disconnect switch should be located where operators and maintenance personnel have quick and easy access to it. In addition to disconnecting electrical power, all other sources of power (pneumatic and hydraulic) should be de-energized before working on a machine or process controlled by a controller.

#### **Safety Circuits**

**ATTENTION:** Explosion Hazard - Do not connect or disconnect connectors while circuit is live unless area is known to be non-hazardous.

Circuits installed on the machine for safety reasons, like overtravel limit switches, stop push buttons, and interlocks, should always be hard-wired directly to the master control relay. These devices must be wired in series so that when any one device opens, the master control relay is de-energized thereby removing power to the machine. Never alter these circuits to defeat their function. Serious injury or machine damage could result.

#### **Power Distribution**

There are some points about power distribution that you should know:

- The master control relay must be able to inhibit all machine motion by removing power to the machine I/O devices when the relay is de-energized.

- If you are using a dc power supply, interrupt the load side rather than the ac line power. This avoids the additional delay of power supply turn-off. The dc power supply should be powered directly from the fused secondary of the transformer. Power to the dc input and output circuits is connected through a set of master control relay contacts.

#### Periodic Tests of Master Control Relay Circuit

Any part can fail, including the switches in a master control relay circuit. The failure of one of these switches would most likely cause an open circuit, which would be a safe power-off failure. However, if one of these switches shorts out, it no longer provides any safety protection. These switches should be tested periodically to assure they will stop machine motion when needed.

# **Power Considerations**

The following explains power considerations for the micro controllers.

#### Isolation Transformers

You may want to use an isolation transformer in the ac line to the controller. This type of transformer provides isolation from your power distribution system and is often used as a step down transformer to reduce line voltage. Any transformer used with the controller must have a sufficient power rating for its load. The power rating is expressed in volt-amperes (VA).

#### **Power Supply Inrush**

The MicroLogix power supply does not require or need a high inrush current. However, if the power source can supply a high inrush current, the MicroLogix power supply will accept it. There is a high level of inrush current when a large capacitor on the input of the MicroLogix is charged up quickly.

If the power source cannot supply high inrush current, the only effect is that the MicroLogix input capacitor charges up more slowly. The following considerations determine whether the power source needs to supply a high inrush current:

- power-up sequence of devices in system

- power source sag if it cannot source inrush current

- the effect of the voltage sag on other equipment

If the power source cannot provide high inrush current when the entire system in an application is powered, the MicroLogix powers-up more slowly. If part of an application's system is already powered and operating when the MicroLogix is powered, the source voltage may sag while the MicroLogix input capacitor is charging. A power source voltage sag can affect other equipment connected to the same power source. For example, a voltage sag may reset a computer connected to the same power source.

#### Loss of Power Source

The power supply is designed to withstand brief power losses without affecting the operation of the system. The time the system is operational during power loss is called "program scan hold-up time after loss of power." The duration of the power supply hold-up time depends on the type and state of the I/O, but is typically between 20 milliseconds and 3 seconds. When the duration of power loss reaches this limit, the power supply signals the processor that it can no longer provide adequate dc power to the system. This is referred to as a power supply shutdown.

#### **Input States on Power Down**

The power supply hold-up time as described above is generally longer than the turn-on and turn-off times of the inputs. Because of this, the input state change from "On" to "Off" that occurs when power is removed may be recorded by the processor before the power supply shuts down the system. Understanding this concept is important. The user program should be written to take this effect into account.

#### **Other Types of Line Conditions**

Occasionally the power source to the system can be temporarily interrupted. It is also possible that the voltage level may drop substantially below the normal line voltage range for a period of time. Both of these conditions are considered to be a loss of power for the system.

# **Preventing Excessive Heat**

For most applications, normal convective cooling keeps the controller within the specified operating range. Ensure that the specified operating range is maintained. Proper spacing of components within an enclosure is usually sufficient for heat dissipation.

In some applications, a substantial amount of heat is produced by other equipment inside or outside the enclosure. In this case, place blower fans inside the enclosure to assist in air circulation and to reduce "hot spots" near the controller.

Additional cooling provisions might be necessary when high ambient temperatures are encountered.

**Note:** Do not bring in unfiltered outside air. Place the controller in an enclosure to protect it from a corrosive atmosphere. Harmful contaminants or dirt could cause improper operation or damage to components. In extreme cases, you may need to use air conditioning to protect against heat build-up within the enclosure.

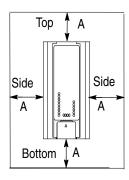

# **Controller Spacing**

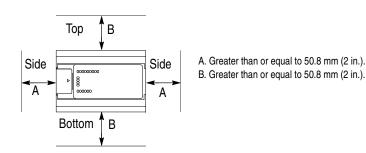

The following figure shows the recommended *minimum* spacing for the controller. (Refer to appendix A for controller dimensions.)

**ATTENTION:** Explosion Hazard - For Class I, Division 2 applications, this product must be installed in an enclosure. All cables connected to the product must remain in the enclosure or be protected by conduit or other means.

# Mounting the Controller

This equipment is suitable for Class I, Division 2, Groups A, B, C, D or non-hazardous locations only, when product or packaging is marked.

**ATTENTION:** Explosion Hazard:

- Substitution of components may impair suitability for Class I, Division 2.

- Be careful of metal chips when drilling mounting holes for your controller. Drilled fragments that fall into the controller could cause damage. Do not drill holes above a mounted controller if the protective wrap is removed.

- Do not replace components or disconnect equipment unless power has been switched off and the area is known to be non-hazardous.

- Do not connect or disconnect connectors while circuit is live unless area is known to be non-hazardous.

- This product must be installed in an enclosure. All cables connected to the product must remain in the enclosure or be protected by conduit or other means.

- The interior of the enclosure must be accessible only by the use of a tool.

- For applicable equipment (for example, relay modules), exposure to some chemicals may degrade the sealing properties of the materials used in these devices:

- Relays, epoxy

It is recommended that you periodically inspect these devices for any degradation of properties and replace the module if degradation is found.

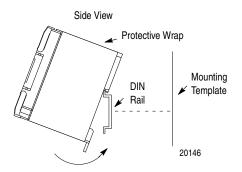

The controller should be mounted horizontally within an enclosure, using a DIN rail or mounting screws.

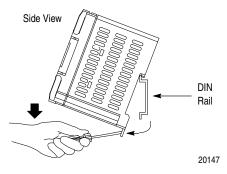

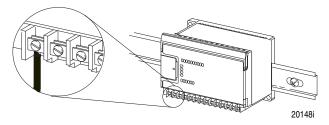

#### **Using a DIN Rail**

Use 35 mm (1.38 in.) DIN rails, such as item number 199–DR1 or 1492–DR5 from Bulletin 1492.

To install your controller on the DIN rail:

- Mount your DIN rail. (Make sure that the placement of the controller on the DIN rail meets the recommended spacing requirements. Refer to controller dimensions in appendix A).

- **2.** Hook the top slot over the DIN rail.

- **3.** While pressing the controller against the rail, snap the controller into position.

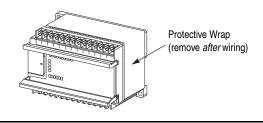

- 4. Leave the protective wrap attached until you are finished wiring the controller.

To remove your controller from the DIN rail:

- 1. Place a screwdriver in the DIN rail latch at the bottom of the controller.

- 2. Holding the controller, pry downward on the latch until the controller is released from the DIN rail.

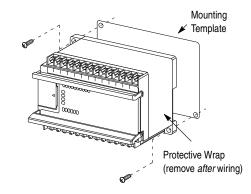

#### **Using Mounting Screws**

To install your controller using mounting screws:

- **Note:** Leave the protective wrap attached until you are finished wiring the controller.

- 1. Use the mounting template from the *MicroLogix 1000 Programmable Controllers Installation Instructions*, publication 1761-5.1.2 or *MicroLogix 1000 (Analog) Programmable Controllers Installation Instructions*, publication 1761-5.1.3, that was shipped with your controller.

- 2. Secure the template to the mounting surface. (Make sure your controller is spaced properly.)

- 3. Drill holes through the template

- 4. Remove the mounting template.

- 5. Mount the controller.

#### **Mounting Your Controller Vertically**

Your controller can also be mounted vertically within an enclosure using mounting screws or a DIN rail. To insure the stability of your controller, we recommend using mounting screws.

To insure the controller's reliability, the following environmental specifications must not be exceeded.

| Description:       | Specification:                                                  |

|--------------------|-----------------------------------------------------------------|

| Operating          | Discrete: $0^{\circ}$ C to +45°C (+32°F to +113°F) <sup>①</sup> |

| Temperature        | Analog: $0^{\circ}$ C to +45°C (+32°F to +113°F) <sup>①</sup>   |

| Operating Shock    | 9.0g peak acceleration (11±-1 ms duration)                      |

| (Panel mounted)    | 3 times each direction, each axis                               |

| Operating Shock    | 7.0g peak acceleration (11±-1 ms duration)                      |

| (DIN rail mounted) | 3 times each direction, each axis                               |

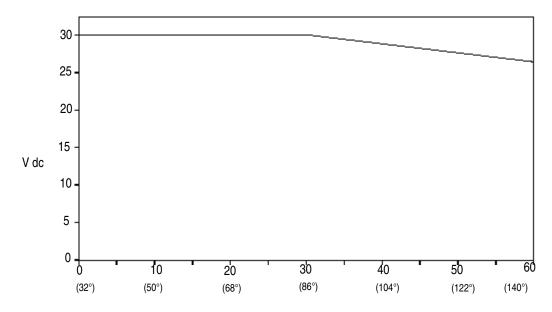

1 DC input voltage derated linearly from +30°C (30V to 26.4V).

**Note:** When mounting your controller vertically, the nameplate should be facing downward.

# **2** Wiring Your Controller

This chapter describes how to wire your controller. Topics include:

- grounding guidelines

- sinking and sourcing circuits

- wiring recommendations

- wiring diagrams, input voltage ranges, and output voltage ranges

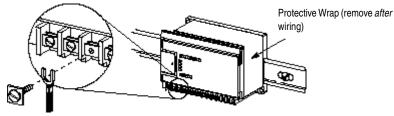

# **Grounding Guidelines**

In solid-state control systems, grounding helps limit the effects of noise due to electromagnetic interference (EMI). Use the heaviest wire gauge listed for wiring your controller with a maximum length of 152.4 mm (6 in.). Run the ground connection from the ground screw of the controller (third screw from left on output terminal rung) to the ground bus.

Note:

This symbol denotes a functional earth ground terminal which provides a low impedance path between electrical circuits and earth for non-safety purposes, such as noise immunity improvement.

**ATTENTION:** All devices that connect to the user 24V power supply or the RS-232 channel must be referenced to chassis ground or floating. Failure to follow this procedure may result in property damage or personal injury.

**ATTENTION:** Chassis ground, user 24V ground, and RS-232 ground are internally connected. You must connect the chassis ground terminal screw to chassis ground prior to connecting any devices.

**ATTENTION:** On the 1761-L10BWB, 1761-L16BWB, 1761-L16BBB, 1761-L20BWB-5A, 1761-L32BBB, and 1761-L32BWB controllers, the user supply 24V dc IN and chassis ground are internally connected.

You must also provide an acceptable grounding path for each device in your application. For more information on proper grounding guidelines, see the *Industrial Automation Wiring and Grounding Guidelines* publication 1770–4.1.

**ATTENTION:** Remove the protective wrap before applying power to the controller. Failure to remove the wrap may cause the controller to overheat.

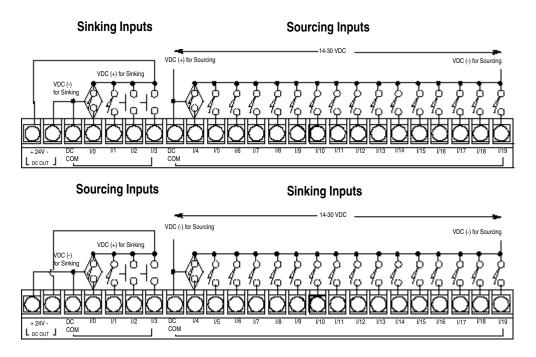

# **Sinking and Sourcing Circuits**

Any of the MicroLogix 1000 DC inputs can be configured as sinking or sourcing depending on how the DC COM is wired on the MicroLogix.

| Туре           | Definition                                                                                                                                                    |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sinking Input  | The input energizes when high-level voltage is applied to the input terminal (active high). Connect the power supply VDC (-) to the MicroLMicroLogix          |

| Sourcing Input | The input energizes when low-level voltage is applied to the input terminal (active low). Connect the power supply VDC (+) to the MicroLogix DC COM terminal. |

### Sinking and Sourcing Wiring Examples

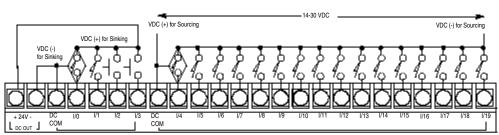

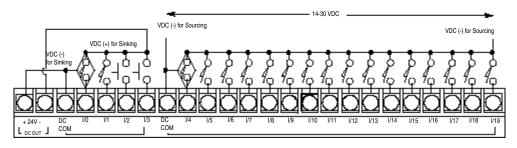

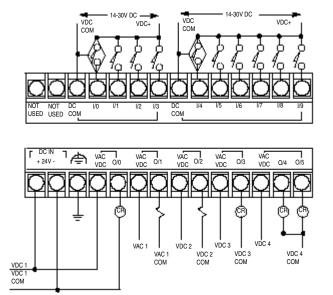

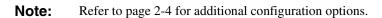

1761-L32BWA (Wiring diagrams also apply to 1761-L20BWA-5A, -L16BWA, -L10BWA.)

Sourcing Inputs

Sinking Inputs

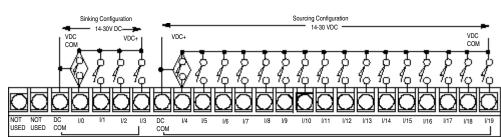

# 1761-L32BWB, -L32BBB (Wiring Diagrams also apply to 1761-L20BWB-5A, -L16BWB, -L10BWB, -L16BBB.)

# Wiring Recommendations

**ATTENTION:** Before you install and wire any device, disconnect power to the controller system.

The following are general recommendations for wiring your controller system.

• Each wire terminal accepts 2 wires of the size listed below:

| Wire Type | Wire Size (2 wire maximum per terminal screw) |

|-----------|-----------------------------------------------|

| Solid     | #14 to #22 AWG                                |

| Stranded  | #16 to #22 AWG                                |

Refer to page 2-25 for wiring your high-speed counter.

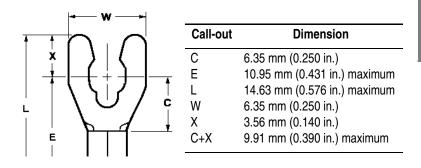

**Note:** The diameter of the terminal screw heads is 5.5 mm (0.220 in.). The input and output terminals of the micro controller are designed for the following spade lugs:

We recommend using either of the following AMP spade lugs: part number 53120-1, if using 22-16 AWG, or part number 53123-1, if using 16-14 AWG.

**Note:** If you use wires without lugs, make sure the wires are securely captured by the pressure plate. This is particularly important at the four end terminal positions where the pressure plate does not touch the outside wall.

**ATTENTION:** Be careful when stripping wires. Wire fragments that fall into the controller could cause damage. Do not strip wires above a mounted controller if the protective wrap is removed.

**ATTENTION:** Remove the protective wrap before applying power to the controller. Failure to remove the wrap may cause the controller to overheat.

**ATTENTION:** Calculate the maximum possible current in each power and common wire. Observe all electrical codes dictating the maximum current allowable for each wire size. Current above the maximum ratings may cause wiring to overheat, which can cause damage.

**ATTENTION:** *United States Only*: If the controller is installed within a potentially hazardous environment, all wiring must comply with the requirements stated in the National Electrical Code 501-4 (b).

- Allow for at least 50 mm (2 in.) between I/O wiring ducts or terminal strips and the controller.

- Route incoming power to the controller by a path separate from the device wiring. Where paths must cross, their intersection should be perpendicular.

**Note:** Do not run signal or communications wiring and power wiring in the same conduit. Wires with different signal characteristics should be routed by separate paths.

- Separate wiring by signal type. Bundle wiring with similar electrical characteristics together.

- Separate input wiring from output wiring.

- Label wiring to all devices in the system. Use tape, shrink-tubing, or other dependable means for labeling purposes. In addition to labeling, use colored insulation to identify wiring based on signal characteristics. For example, you may use blue for dc wiring and red for ac wiring.

# Wiring Diagrams, Discrete Input and Output Voltage Ranges

The following pages show the wiring diagrams, discrete input voltage ranges, and discrete output voltage ranges. Controllers with dc inputs can be wired as either sinking or sourcing configurations. (Sinking and sourcing does not apply to ac inputs.)

Note:

This symbol denotes a functional earth ground terminal which provides a low impedance path between electrical circuits and earth for non-safety purposes, such as noise immunity improvement.

**ATTENTION:** The 24V dc sensor power source should not be used to power output circuits. It should only be used to power input devices (e.g. sensors, switches). Refer to page 2-3 for information on MCR wiring in output circuits.

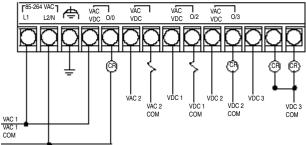

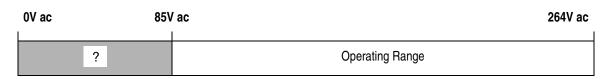

#### 1761-L16AWA Wiring Diagram

#### 1761-L16AWA Input Voltage Range

#### 1761-L16AWA Output Voltage Range

| 0V ac 5V<br>0V dc 5V |                 | 264V ac<br>125V dc |

|----------------------|-----------------|--------------------|

| ?                    | Operating Range |                    |

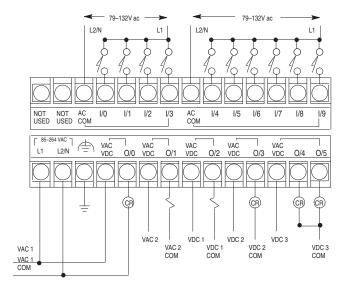

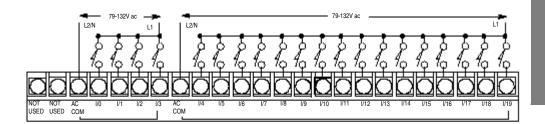

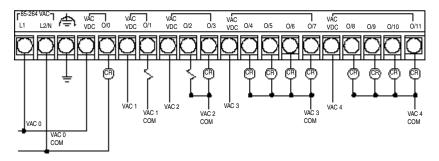

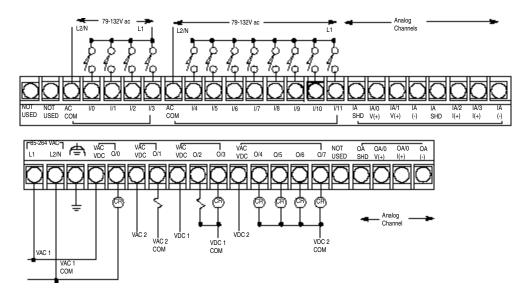

# 1761-L32AWA Wiring Diagram

# 1761-L32AWA Input Voltage Range

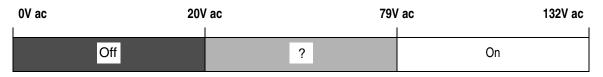

| 0V ac 20\ | / ac 79V | / ac 132V ac |

|-----------|----------|--------------|

| Off       | ?        | On           |

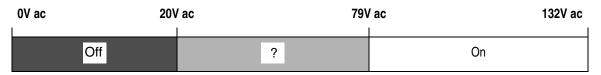

#### 1761-L32AWA Output Voltage Range

| 0V ac | 5V ac | 264V ac         |

|-------|-------|-----------------|

| 0V dc | 5V dc | 125V dc         |

| ?     |       | Operating Range |

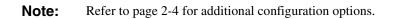

#### 1761-L10BWA Wiring Diagram (Sinking Input Configuration)

**Note:** Refer to page 2-3 for additional configuration options.

#### 1761-L10BWA Input Voltage Range

| 0V dc<br>0V dc | - | dc<br>dc | <br>dc<br>dc | 26.4V dc @ 55°C (131°F)<br>30V dc @ 30°C (86°F) |

|----------------|---|----------|--------------|-------------------------------------------------|

| Off            |   | ?        |              | On                                              |

#### 1761-L10BWA Output Voltage Range

| 0V ac | 5V a |                 | 264V ac |

|-------|------|-----------------|---------|

| 0V dc | 5V a |                 | 125V dc |

| ?     |      | Operating Range |         |

#### 1761-L16BWA Wiring Diagrams (Sinking Input Configuration)

**Note:** Refer to page 2-3 for additional configuration options.

#### 1761-L16BWA Input Voltage Range

| 0V dc<br>0V dc | 5V dc<br>5V dc |   | 14V d<br>14V d |    |

|----------------|----------------|---|----------------|----|

| Off            |                | ? |                | On |

#### 1761-L16BWA Output Voltage Range

| 0V ac 5V<br>0V dc 5V |                 | 264V ac<br>125V dc |

|----------------------|-----------------|--------------------|

| ?                    | Operating Range |                    |

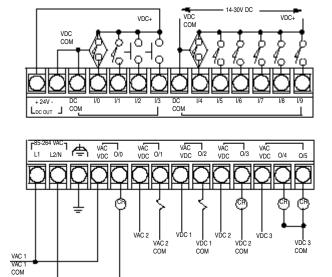

#### 1761-L32BWA Wiring Diagram (Sinking Input Configuration)

**Note:** Refer to page 2-4 for additional configuration options.

#### 1761-L32BWA Input Voltage Range

COM

| 0V dc<br>0V dc | -   | dc<br>dc | 14V<br>14V | 26.4V dc @ 55°C (131°F)<br>30V dc @ 30°C (86°F) |

|----------------|-----|----------|------------|-------------------------------------------------|

| C              | Dff | ?        |            | On                                              |

#### 1761-L32BWA Output Voltage Range

| 0V ac | 5V a |                 | 264V ac |

|-------|------|-----------------|---------|

| 0V dc | 5V c |                 | 125V dc |

| ?     |      | Operating Range |         |

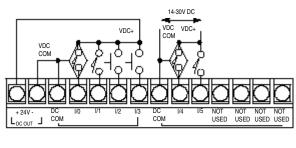

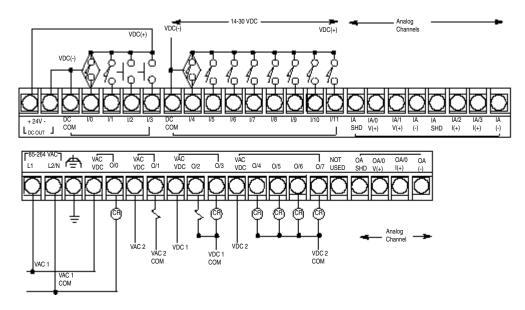

#### 1761-L10BWB Wiring Diagram (Sinking Input Configuration)

#### 1761-L10BWB Input Voltage Range

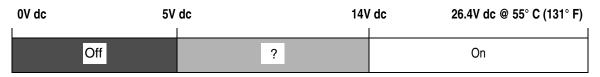

| 0V dc 5V | dc 14V | / dc 26.4V dc | @ 55°C (131°F) |

|----------|--------|---------------|----------------|

| Off      | ?      | On            |                |

#### 1761-L10BWB Output Voltage Range

| 0V ac 5V<br>0V dc 5V |                 |

|----------------------|-----------------|

| ?                    | Operating Range |

#### 1761-L16BWB Wiring Diagram (Sinking Input Configuration)

**Note:** Refer to page 2-4 for additional configuration options.

#### 1761-L16BWB Input Voltage Range

| 0V dc 5V | dc 14\ | / dc 26.4V dc @ | ً₽ 55°C (131°F) |

|----------|--------|-----------------|-----------------|

| Off      | ?      | On              |                 |

#### 1761-L16BWB Output Voltage Range

| 0V ac 5V a<br>0V dc 5V a |                 |

|--------------------------|-----------------|

| ?                        | Operating Range |

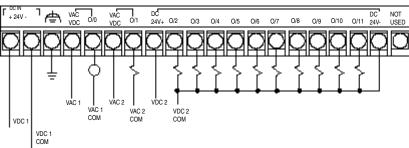

#### 1761-L32BWB Wiring Diagram (Sinking Input Configuration)

Refer to page 2-4 for additional configuration options.

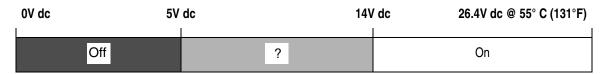

#### 1761-L32BWB Input Voltage Range

Note:

| 0V dc 5\ | / dc 14\ | / dc 26.4V dc @ | ₱ 55° C (131°F) |

|----------|----------|-----------------|-----------------|

| Off      | ?        | On              |                 |

#### 1761-L32BWB Output Voltage Range

| 0V ac | 5V ac | 264V ac         |

|-------|-------|-----------------|

| 0V dc | 5V dc | 125V dc         |

| ?     |       | Operating Range |

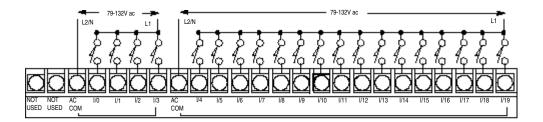

#### 1761-L32AAA Wiring Diagram

#### 1761-L32AAA Input Voltage Range

#### 1761-L32AAA Output Voltage Range

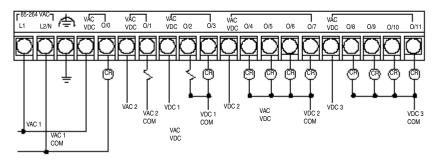

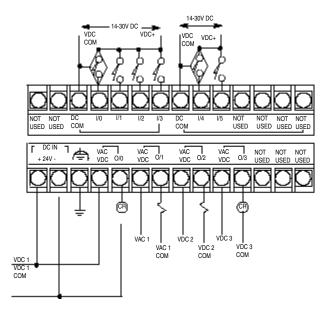

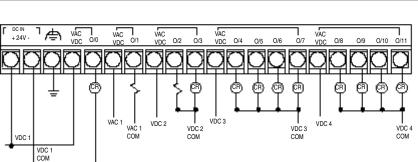

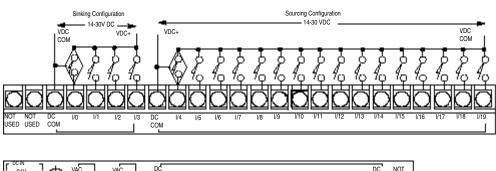

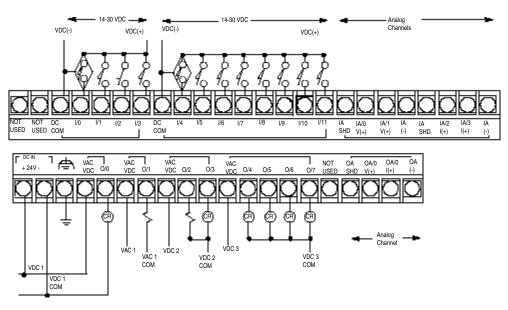

#### 1761-L16BBB Wiring Diagrams (Sinking Input Configuration)

DC VAC VDC VAC VDC DC 24V+ Г DC 24V-合 NOT + 24V -0/0 0/1 0/2 0/3 0/4 O/5 USED VAC 1 VAC 2 VDC 2 VAC 1 COM VAC 2 COM VDC 2 COM VDC 1 VDC 1 COM

#### 1761-L16BBB Input Voltage Range

| 0V dc 51 | / dc 14\ | dc 26.4V dc @ | 55° C (131°F) |

|----------|----------|---------------|---------------|

| Off      | ?        | On            |               |

#### 1761-L16BBB Output Voltage Range

| 0V dc | 20.4 | V dc 26.4V dc   |

|-------|------|-----------------|

|       | ?    | Operating Range |

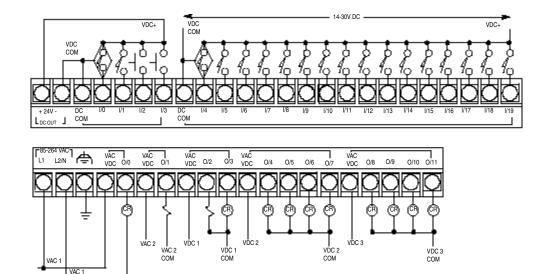

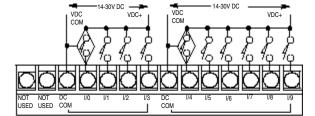

#### 1761-L32BBB Wiring Diagram (Sinking Input Configuration)

**Note:** Refer to page 2-4 for additional configuration options.

#### 1761-L32BBB Input Voltage Range

#### 1761-L32BBB Output Voltage Range

| 0V dc | 20.4 | V dc 26.4V dc   |

|-------|------|-----------------|

|       | ?    | Operating Range |

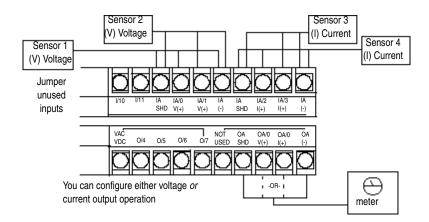

#### 1761-L20AWA-5A Wiring Diagram

**Note:** Refer to pages 2-23 through 2-25 for additional information on analog wiring.

#### 1761-L20AWA-5A Input Voltage Range

| 0V ac 20V | 'ac 79V | ac 132V ac |

|-----------|---------|------------|

| Off       | ?       | On         |

#### 1761-L20AWA-5A Output Voltage Range

| 0V ac 5V<br>0V dc 5V |                 |

|----------------------|-----------------|

| ?                    | Operating Range |

#### 1761-L20BWA-5A Wiring Diagram (Sinking Input Configuration)

**Note:** Refer to page 2-4 for additional discrete configuration options.

Refer to pages 2-23 through 2-25 for additional information on analog wiring.

#### 1761-L20BWA-5A Discrete Input Voltage Range

| 0V dc<br>0V dc | - | dc<br>dc | 14V<br>14V | 26.4V dc @ 55° C (131° F)<br>30V dc @ 30° C (86° F) |

|----------------|---|----------|------------|-----------------------------------------------------|

| Off            | i | ?        |            | On                                                  |

#### 1761-L20BWA-5A Relay Output Voltage Range

| 0V ac 5V | ac              | 264V ac |

|----------|-----------------|---------|

| 0V dc 5V | dc              | 125V dc |

| ?        | Operating Range |         |

#### 1761-L20BWB-5A Wiring Diagram (Sinking Input Configuration)

**Note:** Refer to page 2-4 for additional discrete configuration options.

Refer to pages 2-23 through 2-25 for additional information on analog wiring.

#### 1761-L20BWB-5A Discrete Input Voltage Range

#### 1761-L20BWB-5A Relay Output Voltage Range

|   | ac<br>dc        | 264V ac<br>125V dc |

|---|-----------------|--------------------|

| ? | Operating Range |                    |

### **Minimizing Electrical Noise on Analog Controllers**

Inputs on analog employ digital high frequency filters that significantly reduce the effects of electrical noise on input signals. However, because of the variety of applications and environments where analog controllers are installed and operating, it is impossible to ensure that all environmental noise will be removed by the input filters.

Several specific steps can be taken to help reduce the effects of environmental noise on analog signals:

- install the MicroLogix 1000 system in a properly rated (i.e., NEMA) enclosure. Make sure that the MicroLogix 1000 system is properly grounded.

- use Belden cable #8761 for wiring the analog channels making sure that the drain wire and foil shield are properly earth grounded at one end of the cable.

- route the Belden cable separate from any other wiring. Additional noise immunity can be obtained by routing the cables in grounded conduit.

A system may malfunction due to a change in the operating environment after a period of time. We recommend periodically checking system operation, particularly when new machinery or other noise sources are installed near the MicroLogix 1000 system.

# **Grounding Your Analog Cable**

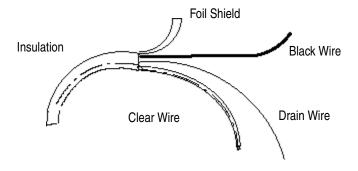

Use shielded communication cable (Belden #8761). The Belden cable has two signal wires (black and clear), one drain wire and a foil shield. The drain wire and foil shield must be grounded at one end of the cable. *Do not* earth ground the drain wire and foil shield at *both* ends of the cable.

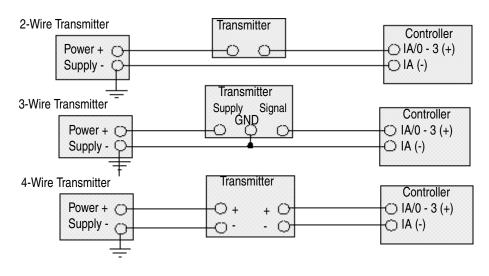

# Wiring Your Analog Channels

Analog input circuits can monitor current *and* voltage signals and convert them to serial digital data. The analog output can support either a voltage *or* a current function.

For increased noise immunity, connect a ground wire directly from the shield terminals to chassis ground.

Important:

The controller does *not* provide loop power for analog inputs. Use a power supply that matches the transmitter specifications.

# **Analog Voltage and Current Input and Output Ranges**

#### **Analog Voltage Input Range**

| -24V dc -1 | 0.5V dc         | 10.5V dc  |  |

|------------|-----------------|-----------|--|

| Underrange | Operating Range | Overrange |  |

#### **Analog Current Input Range**

| -50mA -21  | mA 21           | mA 50 mA  |

|------------|-----------------|-----------|

| Underrange | Operating Range | Overrange |

**Note:** The analog voltage inputs are protected to withstand the application of  $\pm 24V$  dc without damage to the controller. The analog current inputs are protected to withstand the application of  $\pm 50$  mA without damage.

#### **Analog Voltage Output Range**

#### **Analog Current Output Range**

**Note:** *The analog outputs are protected to withstand the short circuiting of the voltage or current outputs without damage to the controller.*

For information on analog signal and data word values using the nominal transfer function formula, see page 5-5.

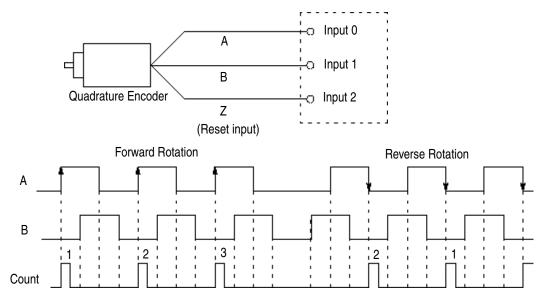

# Wiring Your Controller for High-Speed Counter Applications

To wire the controller for high-speed counter applications use input terminals I/0, I/1, I/2, and I/3. Refer to chapter 12 for information on using the high-speed counter.

Shielded cable is required for high-speed input signals 0-3 when the filter setting is set to either 0.10 ms or 0.075 ms. We recommend Belden #9503 or equivalent for lengths up to 305 m (1000 ft). Shields should be grounded only at the signal source end of the cable. Ground the shield to the case of the signal source, so energy coupled to the shield will not be delivered to signal source's electronics.

Notes:

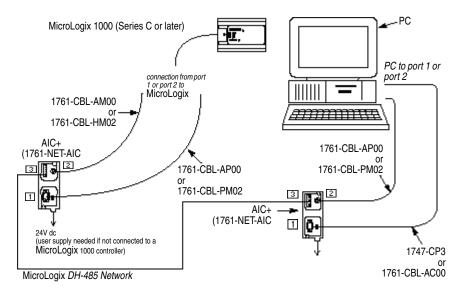

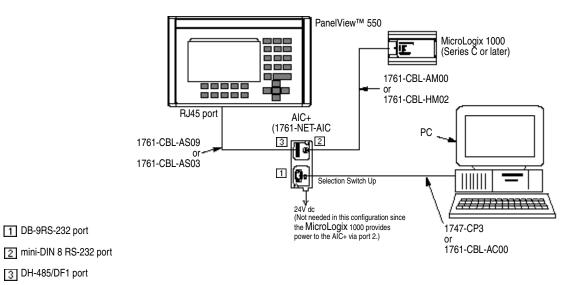

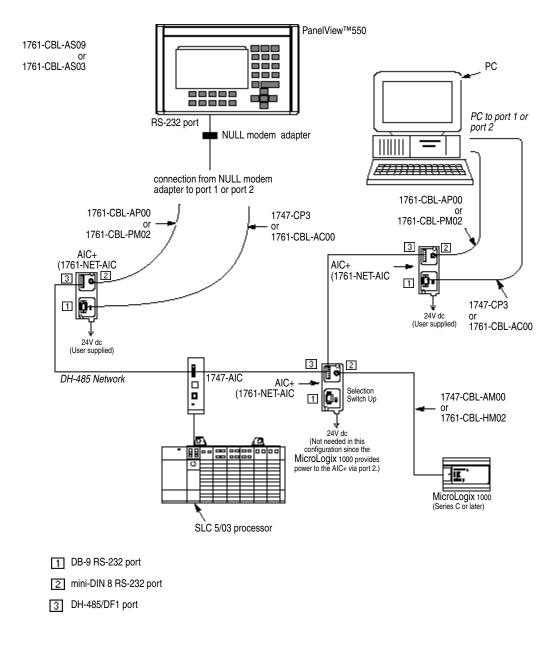

# **3** Connecting the System

This chapter describes how to wire your controller system. The method you use and cabling required to connect your controller depends on what type of system you are employing. This chapter also describes how the controller establishes communication with the appropriate network.

| For information on:        | See page: |

|----------------------------|-----------|

| DF1 protocol connections   | 3-2       |

| DH-485 network connections | 3-6       |

| Establishing communication | 3-19      |

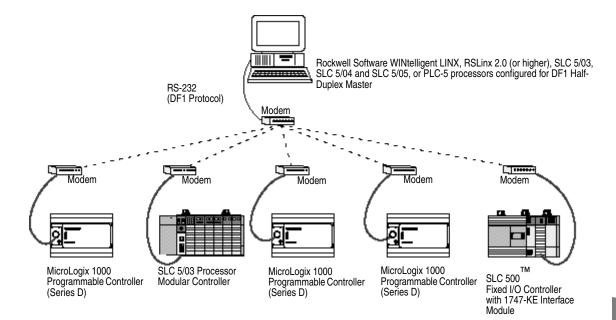

# **Connecting the DF1 Protocol**

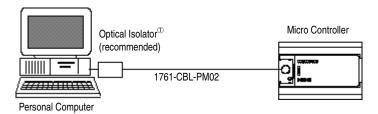

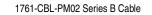

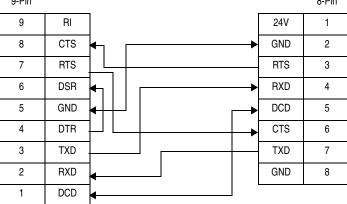

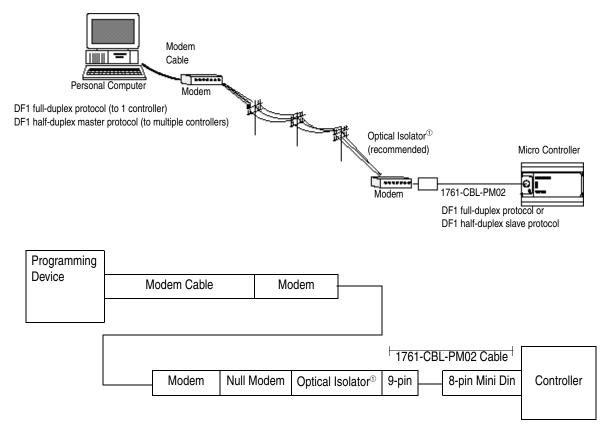

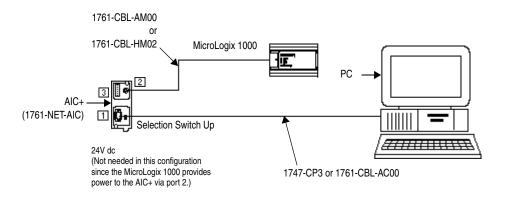

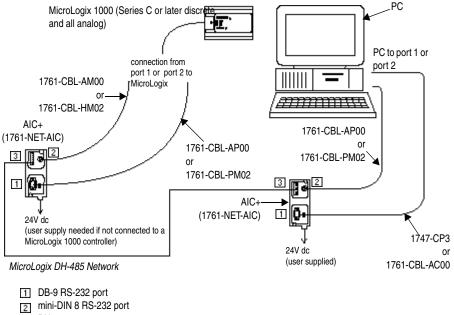

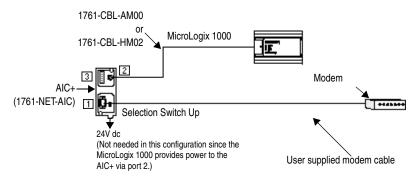

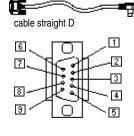

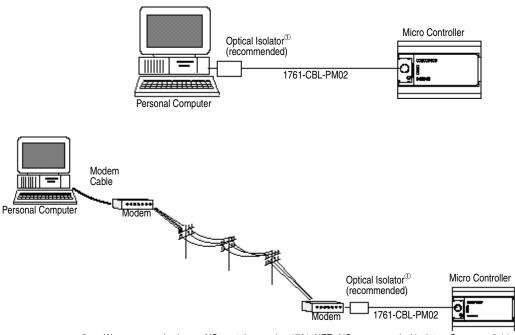

There are two ways to connect the MicroLogix 1000 programmable controller to your personal computer using the DF1 protocol: using an isolated point-to-point connection, or using a modem. Descriptions of these methods follow.